https://chacker.pl/

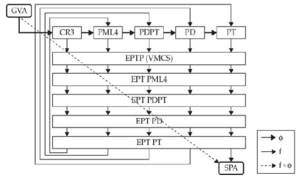

Widzieliśmy, jak można wdrożyć stronicowanie w tle na istniejącym mechanizmie stronicowania, aby wirtualizować MMU. Stronicowanie w tle jest złożone, a aktualizacje tablic stron są kosztowne; dlatego, aby poprawić tę sytuację, opracowano nową technologię wspomaganą sprzętowo, znaną jako Second Level Address Translation (SLAT). Intel implementuje SLAT z Extended Page Tables (EPT29). W skrócie, EPT działa jak tablice stron; różnica polega na tym, że podczas gdy tablice stron tłumaczą VA na PA, EPT tłumaczy GPA na SPA. VMM działający w trybie głównym VMX musi skonfigurować i utrzymywać zestaw wielopoziomowych tablic stron EPT, które są używane do tłumaczenia GPA na SPA. Wskaźnik EPT najwyższego poziomu (EPTP30) jest przechowywany w jednym z pól sterujących VMCS. Z perspektywy gościa nadal używamy tablic stron jak zwykle, aby tłumaczyć VA na PA; w rzeczywistości są to GVA i GPA. Aby uzyskać dostęp do strony, procesor najpierw przechodzi przez tabele stron gościa, aby uzyskać GPA z jego GVA; następnie przechodzi przez tabele EPT (które są niewidoczne dla gościa), aby uzyskać SPA z GPA. Jeśli przypomnimy sobie sprzętowy wirtualizator Goldberga, moglibyśmy zobaczyć tabele stron jako mapę ϕ, a EPT jako mapę f. Tłumaczenie GVA na SPA jest wykonywane przez złożoną mapę „f ° ϕ”. Należy pamiętać, że gdy procesor przechodzi przez wielopoziomowe tabele stron gościa, każdy poziom (w trybie długim: PML4, PDPT, PD, PT) wskazuje na następny przez swój GPA, co oznacza, że każdy poziom tabeli stron musi zostać przetłumaczony przez mechanizm EPT. Jest to znane jako „dwuwymiarowe przejście strony”, a w najgorszym przypadku (gdy każdy krok tłumaczenia powoduje brak pamięci podręcznej) do przetłumaczenia GVA potrzeba 24 obciążeń pamięci. Nawet jeśli translacja adresów może być droższa niż w przypadku stronicowania w tle, największą zaletą EPT jest to, że aktualizacje tablicy stron są bezpośrednie, co zmniejsza liczbę pułapek i upraszcza implementację VMM.

Podobnie jak w przypadku tabel stron, EPT umożliwia mapowanie adresu na nieistniejącą stronę fizyczną. Próba dostępu w tym przypadku spowoduje wyjście maszyny wirtualnej. Podstawowym powodem wyjścia dla tego rodzaju pułapki jest naruszenie EPT.32 Ponadto pola kwalifikacji wyjścia i adresu fizycznego gościa są ustawione. W niektórych przypadkach EPT może nie być całkowicie niewidoczne dla gości; w celu poprawy wydajności niektóre funkcje związane z EPT mogą być udostępnione maszynom wirtualnym. Jedną z tych funkcji jest funkcja przełączania EPT (wywoływana za pomocą instrukcji VMFUNC), która umożliwia gościowi jawne przełączanie swojego EPTP z listy wartości ustalonych przez VMM. Inną ważną funkcją są wyjątki wirtualizacji (#VE34). Jak sama nazwa wskazuje, funkcja ta może być używana do dostarczania wyjątków związanych z wirtualizacją do gościa za pośrednictwem wektora IDT 20. Ta funkcja może być używana razem z naruszeniami konwertowalnego EPT, więc gdy dochodzi do naruszenia EPT, nie powoduje to wyjścia maszyny wirtualnej. Zamiast tego gość otrzymuje komunikat #VE, który go obsługuje, dzięki czemu unika się pułapek w VMM.

![]()