https://chacker.pl/

Protokół Universal Asynchronous Receiver-Transmitter umożliwia dwóm urządzeniom komunikację szeregową przez kanał komunikacyjny. UART jest powszechnie używany do łączenia się z konsolą, aby umożliwić człowiekowi interakcję z urządzeniem. Chociaż większość urządzeń nie będzie miała zewnętrznie dostępnego interfejsu do komunikacji szeregowej, wiele będzie miało wewnętrzny interfejs, który był używany podczas opracowywania i testowania urządzenia. Podczas przeprowadzania testów urządzeń znalazłem zarówno uwierzytelnione, jak i nieuwierzytelnione konsole na wewnętrznie dostępnych interfejsach szeregowych. UART wymaga trzech pinów do komunikacji i zwykle występuje w grupie czterech pinów .

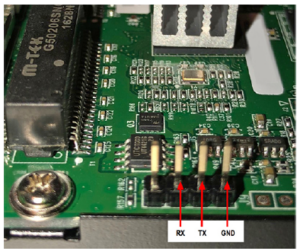

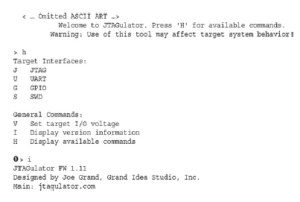

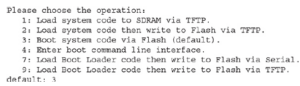

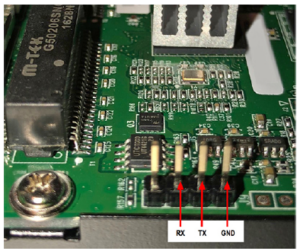

Na płytce możesz zobaczyć etykiety, ale zazwyczaj te pady lub nagłówki nie są oznaczone i trzeba je odkryć. Chociaż Rysunek pokazuje ładny przykład, w którym nagłówki wyróżniają się jako kandydaci do komunikacji szeregowej, układ pinów może nie zawsze być tak prosty i może być pomieszany w większej liczbie pinów. Głównym powodem lokalizowania i łączenia się z wewnętrznymi portami szeregowymi jest próba zlokalizowania informacji, które nie miały być dostępne dla użytkownika systemu. Na przykład interfejs sieciowy zazwyczaj nie zapewnia bezpośredniego dostępu do systemu plików, ale konsola szeregowa w systemie opartym na systemie Linux zapewni użytkownikowi dostęp do systemu plików. Gdy port szeregowy zostanie uwierzytelniony, będziesz musiał brutalnie wymusić poświadczenia lub spróbować ominąć uwierzytelnianie, zmieniając proces rozruchu (potencjalnie za pomocą portu debugowania JTAG). Aby odkryć pady szeregowe, można użyć narzędzia takiego jak JTAGulator, opracowanego przez Joe Granda, aby uzyskać sygnały metodą brute-force i uzyskać układ padów oraz szybkość transmisji. Poniżej znajduje się przykład uruchomienia testu identyfikacji UART na Ubiquiti ER-X pokazanym na rysunku 20-1, gdzie oznaczone piny zostały zidentyfikowane za pomocą JTAGulatora. Oto kroki:

- Zlokalizuj nagłówki lub pady, które Twoim zdaniem mogą być UART, poprzez sprawdzenie płytki. (Widzenie dwóch do czterech padów/pinów zgrupowanych razem na płytce to dobry znak, ale jak wspomniano wcześniej, mogą być one przeplatane z innymi funkcjonalnymi padami/pinami.)

- Odkryj napięcie docelowe, badając płytkę multimetrem lub identyfikując układ scalony i sprawdzając arkusz danych.

- Odkryj uziemienie, do którego łatwo się podłączyć, mierząc rezystancję (omy) między znanym uziemieniem (takim jak uziemienie obudowy) a pinami, do których łatwo się podłączyć (efektywnie 0 omów między znanym uziemieniem a danym pinem).

- Podłącz płytkę do JTAGulatora, jeśli masz wystarczająco dużo szczęścia, aby znaleźć nagłówki, lub przylutuj nagłówek do płytki, a następnie podłącz.

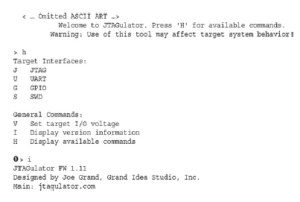

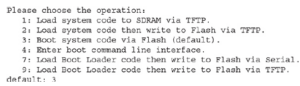

- Sprawdź wersję oprogramowania układowego JTAGulatora (1). Wersję można sprawdzić w oparciu o kod w repozytorium pod adresem https://github.com/grandideastudio/jtagulator/releases. Jeśli wersja nie jest najnowsza, postępuj zgodnie z instrukcjami na stronie www.youtube.com/watch? v=xlXwy-weG1M.

- Włącz tryb UART (2) i ustaw napięcie docelowe (3).

- Uruchom test identyfikacji UART (4).

- W przypadku powodzenia poszukaj rozsądnych odpowiedzi, takich jak powrót karetki, przesunięcie wiersza lub czytelny tekst (5) (synchronizacja l-timers(q)).

9. Zweryfikuj zidentyfikowane ustawienia, uruchamiając w trybie pass-thru (6) z kandydatem na szybkość transmisji (7) 57600 w naszym przypadku).

Na płytce możesz zobaczyć etykiety, ale zazwyczaj te pady lub nagłówki nie są oznaczone i trzeba je odkryć. Chociaż Rysunek pokazuje ładny przykład, w którym nagłówki wyróżniają się jako kandydaci do komunikacji szeregowej, układ pinów może nie zawsze być tak prosty i może być pomieszany w większej liczbie pinów. Głównym powodem lokalizowania i łączenia się z wewnętrznymi portami szeregowymi jest próba zlokalizowania informacji, które nie miały być dostępne dla użytkownika systemu. Na przykład interfejs sieciowy zazwyczaj nie zapewnia bezpośredniego dostępu do systemu plików, ale konsola szeregowa w systemie opartym na systemie Linux zapewni użytkownikowi dostęp do systemu plików. Gdy port szeregowy zostanie uwierzytelniony, będziesz musiał brutalnie wymusić poświadczenia lub spróbować ominąć uwierzytelnianie, zmieniając proces rozruchu (potencjalnie za pomocą portu debugowania JTAG). Aby odkryć pady szeregowe, można użyć narzędzia takiego jak JTAGulator, opracowanego przez Joe Granda, aby uzyskać sygnały metodą brute-force i uzyskać układ padów oraz szybkość transmisji. Poniżej znajduje się przykład uruchomienia testu identyfikacji UART na Ubiquiti ER-X pokazanym na rysunku 20-1, gdzie oznaczone piny zostały zidentyfikowane za pomocą JTAGulatora. Oto kroki:

- Zlokalizuj nagłówki lub pady, które Twoim zdaniem mogą być UART, poprzez sprawdzenie płytki. (Widzenie dwóch do czterech padów/pinów zgrupowanych razem na płytce to dobry znak, ale jak wspomniano wcześniej, mogą być one przeplatane z innymi funkcjonalnymi padami/pinami.)

- Odkryj napięcie docelowe, badając płytkę multimetrem lub identyfikując układ scalony i sprawdzając arkusz danych.

- Odkryj uziemienie, do którego łatwo się podłączyć, mierząc rezystancję (omy) między znanym uziemieniem (takim jak uziemienie obudowy) a pinami, do których łatwo się podłączyć (efektywnie 0 omów między znanym uziemieniem a danym pinem).

- Podłącz płytkę do JTAGulatora, jeśli masz wystarczająco dużo szczęścia, aby znaleźć nagłówki, lub przylutuj nagłówek do płytki, a następnie podłącz.

- Sprawdź wersję oprogramowania układowego JTAGulatora (1). Wersję można sprawdzić w oparciu o kod w repozytorium pod adresem https://github.com/grandideastudio/jtagulator/releases. Jeśli wersja nie jest najnowsza, postępuj zgodnie z instrukcjami na stronie www.youtube.com/watch? v=xlXwy-weG1M.

- Włącz tryb UART (2) i ustaw napięcie docelowe (3).

- Uruchom test identyfikacji UART (4).

- W przypadku powodzenia poszukaj rozsądnych odpowiedzi, takich jak powrót karetki, przesunięcie wiersza lub czytelny tekst (5) (synchronizacja l-timers(q)).

9. Zweryfikuj zidentyfikowane ustawienia, uruchamiając w trybie pass-thru (6) z kandydatem na szybkość transmisji (7) 57600 w naszym przypadku).

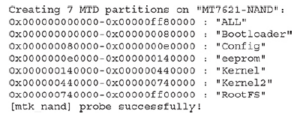

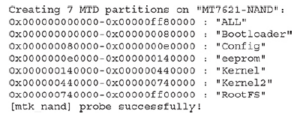

- Działa na systemie Linux w wersji 3.10.14-UBNT:

- Partycje MTD pomagają zrozumieć układ pamięci masowej:

Po ustaleniu układu możesz użyć narzędzia takiego jak Bus Pirate, aby połączyć się z padami i komunikować się z systemem wbudowanym. Najważniejszą rzeczą do zapamiętania jest podłączenie TX na urządzeniu do RX Twojego Bus Pirate i podłączenie RX na urządzeniu do TX Twojego Bus Pirate. Podobnie jak w przypadku interfejsu JTAG, niektórzy mogą bagatelizować powagę włączenia portów szeregowych na urządzeniu. Jednak dzięki dostępowi do konsoli atakujący może wyodrębnić konfigurację i pliki binarne, zainstalować narzędzia i poszukać globalnych sekretów, które ułatwiają zdalne ataki na wszystkie urządzenia tego typu.